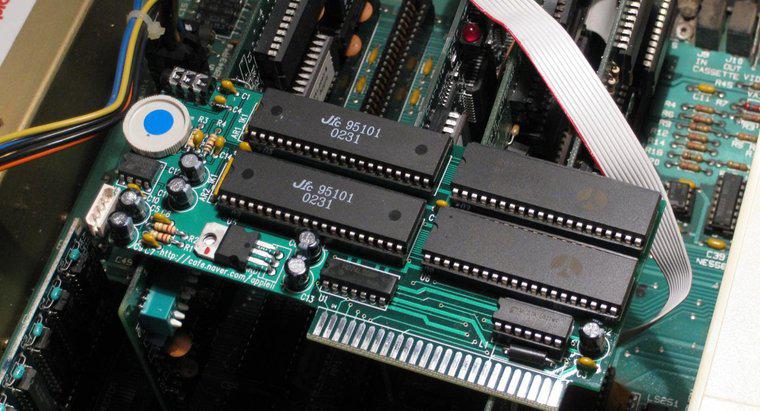

Las diferencias básicas entre CMOS y la lógica TTL incluyen que los componentes CMOS son más caros, que los circuitos CMOS no consumen tanta potencia y el consumo de energía TTL aumenta más lentamente. Otras diferencias incluyen la transmisión de señales digitales y daños susceptibilidad.

Los componentes TTL son generalmente menos costosos que los componentes CMOS. Sin embargo, debido a chips más pequeños, el CMOS es generalmente menos costoso en el nivel del sistema. Cuando están en reposo, los circuitos CMOS no consumen tanta energía como los circuitos TTL. Sin embargo, las velocidades de reloj más altas hacen que el consumo de energía del CMOS aumente a una velocidad mayor que la del TTL. Es más probable que los componentes CMOS se dañen con la descarga electrostática que los componentes TTL. Las señales digitales son más económicas y más simples con los chips CMOS debido a los tiempos de subida y caída más largos.

La disipación de potencia de CMOS es generalmente de 10 nW por compuerta, mientras que la disipación de potencia de TTL suele ser de 10 mW por compuerta. Los retrasos de propagación de TTL son generalmente de 10 nS, mientras que los retrasos de propagación de CMOS generalmente están entre 25 nS y 50 nS.

El rango de nivel de voltaje para TTL es generalmente de 4.75V - 5.25V. El rango de nivel de voltaje para CMOS varía de 0 a 1/3 VDD en un nivel bajo y de 2/3 VDD a VDD en un nivel alto.